"Lucian Blaga" University of Sibiu "Hermann Oberth" Engineering Faculty Computer Science Department

# Advanced Prediction Methods Integrated Into Speculative Computer Architectures

PhD Thesis

Abstract

Author: Árpád GELLÉRT, MSc

PhD Supervisor: Professor Lucian N. VINȚAN, PhD

PhD Co-supervisor: Professor Theo UNGERER, PhD

SIBIU, 2008

Universitatea "Lucian Blaga" din Sibiu Facultatea de inginerie "Hermann Oberth" Catedra de Calculatoare și Automatizări

# Metode avansate de predicție integrate în arhitecturi cu procesări speculative

Teză de doctorat

Rezumat

Autor: Asist. univ. ing. Árpád GELLÉRT, MSc

Conducători științifici: Prof. univ. dr. ing. Lucian N. VINȚAN Prof. univ. dr. Theo UNGERER (cotutelă)

SIBIU, 2008

# Mulțumiri

În primul rând doresc să mulțumesc conducătorului meu de doctorat prof. univ. dr. ing. Lucian VINȚAN, pentru încrederea acordată, pentru deosebita responsabilitate a coordonării sale științifice, pentru discuțiile profesionale extrem de stimulative pe care le-am avut și pentru întreg sprijinul acordat cu multă generozitate. De asemenea, mulțumesc conducătorului de doctorat prin cotutelă, prof. dr. Theo UNGERER de la Universitatea din Augsburg, Germania, pentru discuțiile utile și pentru sprijinul oferit. Țin să mulțumesc colegului meu dr. Adrian FLOREA pentru ajutorul acordat și pentru sfaturile sale deosebit de utile. Mulțumesc și d-lui Dr. Colin EGAN de la Universitatea din Hertfordshire pentru colaborarea sa precum și pentru observațiile și sugestiile făcute. De asemenea, doresc să mulțumesc colegilor de la Catedra de Calculatoare și Automatizări din cadrul Universității "Lucian Blaga" pentru sprijinul acordat și pentru climatul favorabil asigurat. Nu în ultimul rând, doresc să mulțumesc familiei pentru sprijinul necontenit și pentru răbdarea de care a dat dovadă în această perioadă.

Cercetările prezentate în această lucrare au fost parțial susținute prin granturile CNCSIS TD-248/2007-2008 și A-39/2007-2008 respectiv prin proiectul HPC-EUROPA (RII3-CT-2003-506079) din cadrul programului FP6 "Structuring the European Research Area", cu suportul Comunității Europene (Research Infrastructure Action).

Paralelismul la nivelul instrucțiunilor este limitat de dependențele existente între instrucțiuni, iar pentru eliminarea lor microprocesoarele moderne, unele din ele prezentate în Capitolul 2, folosesc tehnici speculative. Principalul obiectiv al acestei teze îl reprezintă creșterea performanțelor unor microarhitecturi superscalare și SMT (Simultaneous Multithreading) prin tehnici anticipatorii dinamice precum predicția branch-urilor, predicția valorilor și reutilizarea instrucțiunilor. Această lucrare aduce contribuții originale în identificarea branch-urilor dificile și îmbunătățirea predictibilității lor, în caracterizarea comportamentului acestora din punct de vedere al gradului de aleatorism, respectiv în dezvoltarea unor tehnici de reutilizare și predicție selective a valorilor instrucțiunilor în cadrul arhitecturilor superscalare și al celor cu fire multiple de execuție.

Instructionile de ramificatie, generate de constructii de limbaj de tipul if, switch, for, while etc., reprezintă un obstacol major în exploatarea paralelismului la nivelul instrucțiunilor (ILP). Rezultate statistice bazate pe simulări laborioase pe benchmark-uri reprezentative arată că o instrucțiune de ramificație apare la fiecare 5 – 8 instrucțiuni executate, ceea ce înseamnă că rata de aducere a instrucțiunilor este limitată la cel mult 8, aducerea simultană a mai multor instructiuni fiind inutilă. Pentru cresterea gradului de paralelism la nivelul instructiunilor procesoarele moderne folosesc predictoare markoviene, neuronale, bayesiene, bazate pe arbori de decizie sau pe algoritmi de tipul support vector machine etc., simplificate pentru a putea fi implementate în hardware. Prin predictia dinamică a branch-urilor pot fi procesate mai multe basic block-uri în paralel. Pentru îmbunătătirea performantei instructiunile de ramificatie trebuie identificate și atât direcția cât și adresa de salt trebuie predicționate corect. Factorul de superscalaritate al microprocesoarelor devine din ce în ce mai mare, permitând rate de procesare mai agresive pentru îmbunătătirea performantelor. Procesoarele cu factor mare de superscalaritate pot fi afectate din punct de vedere al performantelor în cazul predicțiilor greșite când contextul CPU trebuie refăcut și instrucțiunile trebuie reexecutate pe căile corecte. De aceea, performanta globală depinde foarte mult de acuratetea predictorului de salturi. Având în vedere faptul că numărul de instrucțiuni executate per ciclu crește neliniar cu acuratețea predicției, este foarte importantă îmbunătățirea acurateții predictoarelor actuale. Calitatea unui model de predictie este dependentă de calitatea informatiei disponibile. Este foarte importantă alegerea caracteristicilor pe baza cărora se generează predictia. Marea majoritate a predictoarelor de salturi se bazează pe mai multe informatii de intrare (adresa instructiunii de salt, istoria locală, istoria globală, informatii de cale etc.) fără să tină cont de cauzele reale (ex. instructiuni de salt nepolarizate) care produc o acuratete scăzută și implicit performante mai slabe.

În Capitolul 3 am demonstrat că o instrucțiune de ramificație într-un anumit context dinamic al informației de predicție este greu de prezis dacă este nepolarizată în acel context, oscilând între *taken* (saltul se face) respectiv *not taken* (saltul nu se face) într-un mod nedeterminist, entropic (comportament dezordonat). Cu alte cuvinte, o instrucțiune de ramificație dinamică este nepredictibilă cu o anumită informație de predicție, dacă este nepolarizată în contextul dinamic considerat și comportamentul în acel context nu poate fi modelat prin procese stohastice Markov. Am identificat aceste branch-uri dificile și am încercat îmbunătățirea predictibilității lor prin extinderea informației de predicție. Pe baza unor simulări laborioase am arătat că procentajul branch-urilor nepolarizate, pe istoria locală și globală, este semnificativ: în medie între 6% și 24% pe benchmark-urile SPEC 2000, în funcție de contextul de predicție folosit și de lungimea acestuia (16-28 biți). De asemenea, cercetările noastre au arătat că adăugarea informației de cale (formată din PC-urile ultimelor *k* branch-uri) la cele clasice de istorie locală/globală determină o polarizare mai ridicată doar în cazul folosirii unor contexte de

istorie locală/globală scurte (sub 16 biți). Istoriile locale și globale suficient de lungi aproximează foarte bine informația de cale.

În Capitolul 4 am arătat că pentru anumite instrucțiuni de ramificație, informațiile de predicție limitate (istorie locală, istorie globală și calea spre branch-ul supus predicției) folosite de predictoarele actuale nu sunt întotdeauna suficient de relevante si, din această cauză, ele nu pot fi predicționate cu acuratețe. Acuratețea cea mai ridicată pe branch-urile nepolarizate, de doar 77,30%, am obtinut-o cu piecewise linear branch predictor [Jim05]. De aceea, este deosebit de importantă găsirea unor informații relevante care determină comportamentul instructiunilor de ramificație, pentru a fi utilizate de predictoare mai eficiente. Am dezvoltat diferite predictoare de valori Markoviene care folosesc istoria comprimată a precedentelor conditii de salt, ale cărei elemente pot fi -1, 0 sau 1, în funcție de semnul diferentei dintre operanzi. Nici aceste predictoare puternice, capabile să exploateze corelația dintre comportamentul branch-ului și istoria conditiilor, n-au reusit să îmbunătătească predictibilitatea acestor branch-uri dificile. De asemenea, am îmbunătătit predictoare conventionale (GAg, PAg) și neuronale, prin utilizarea condiției de salt precedente - Previous Branch Condition (PBC) - sub forma unei diferențe pe 32 de biți dintre operanzi. Chiar și predictorul piecewise linear branch predictor îmbunătățit, cel mai performant pe branch-urile nepolarizate, obtine o acuratete modestă de 78,3% pe branchurile nepolarizate, în timp ce acuratețea globală a predicției este de 95,45%. Așadar, branch-urile nepolarizate sunt caracterizate de acurateți de predicție scăzute, indiferent de informația de predictie folosită, reprezentând astfel o limitare fundamentală în domeniul predictiei branchurilor. Astfel, cresterea acuratetii de predictie a acestor instructiuni de ramificatie nepolarizate constituie o problemă deschisă, deoarece fiecare procent de astfel de instructiuni reduce decisiv acuratetea predictiei și implicit performanta de procesare.

Pornind de la această provocare tehnică, în Capitolul 5 am realizat un studiu comparativ privind gradul de aleatorism al secventelor de simboluri (taken si not taken) generate de branchuri polarizate respectiv nepolarizate. Pe baza cercetării bibliografice efectuate, am dezvoltat patru metrici pentru caracterizarea comportamentului unui branch din punct de vedere al gradului de aleatorism: complexitatea Kolmogorov a secvenței de program care generează branch-ul, rata de compresie, entropia discretă respectiv acuratețea de predicție cu HMM (Hidden Markov Models) a secventei generate de branch. Rezultatele simulărilor efectuate pe sase benchmark-uri de numere întregi din suita SPEC 2000 arată că toate cele patru metrici de caracterizare intrinsecă a unei secvențe binare din punct de vedere al gradului de aleatorism asociat, converg în aceeasi directie. Ele sunt foarte utile arhitectului de microprocesoare întrucât arată dacă un anumit branch dinamic este sau nu este "aleator" sau "nepredictibil". În cazul în care metricile utilizate arată în mod clar că branch-ul nu este unul intrinsec aleator, arhitectul are sanse reale de îmbunătătire a predictorului aferent. În cazul aleatorismului ridicat, răspunsul este unul pesimist întrucât secventa este una intrinsec, și deci iremediabil, aleatoare. De precizat că aleatorismul comportării acestor branch-uri este o consecintă a complexitătii uriase a programelor care le generează, după cum arătăm în lucrare.

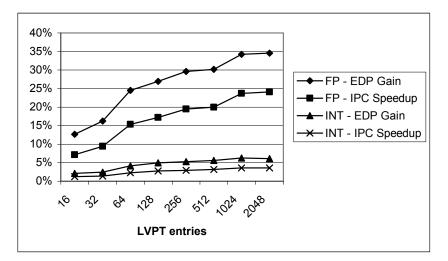

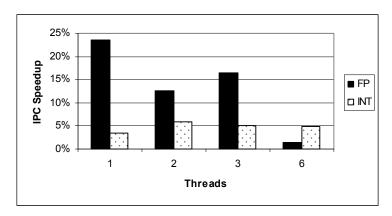

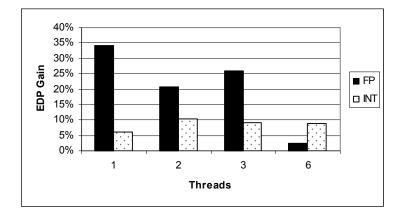

Instrucțiunile cu latență ridicată reprezintă o altă sursă de limitare a paralelismului la nivelul instrucțiunilor. În Capitolul 6 am arătat că 28,68% din instrucțiunile de ramificație (5,61% fiind chiar nepolarizate) sunt dependente de instrucțiuni cu latență ridicată (Load-uri critice, înmulțiri, împărțiri). Aceste dependențe reprezintă o sursă importantă de penalități datorate predicțiilor greșite, afectând serios performanța globală a procesorului. De aceea, impactul negativ al branch-urilor, în special al celor nepolarizate, asupra performanței globale poate fi atenuat anticipând rezultatele instrucțiunilor cu latență ridicată. Am dezvoltat un mecanism de anticipare selectivă a valorilor instrucțiunilor cu latență de execuție ridicată, care include o schemă de reutilizare pentru instrucțiunile Mul și Div, respectiv un predictor de valori pentru instrucțiunile Load critice. Rezultatele simulărilor efectuate, au arătat creșteri de performanță (IPC) de 3,5% pe benchmark-urile de numere întregi respectiv 23,6% pe cele flotante și o scădere importantă a consumului relativ de energie (a EDP-ului) de 6,2% respectiv 34,5%.

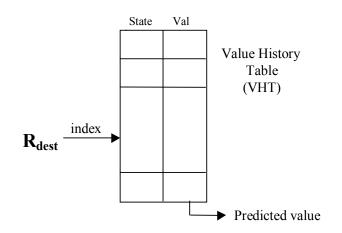

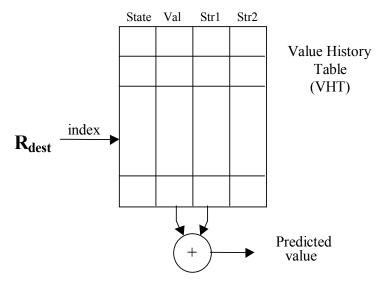

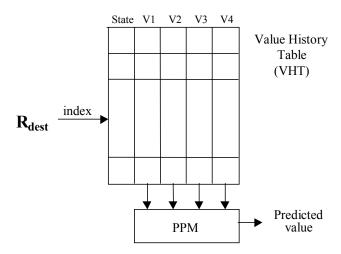

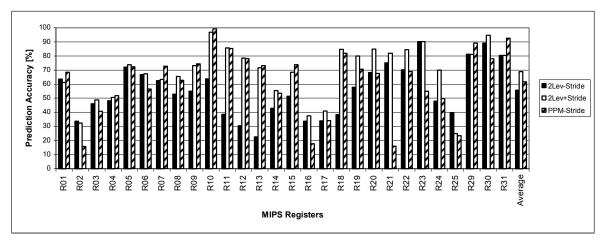

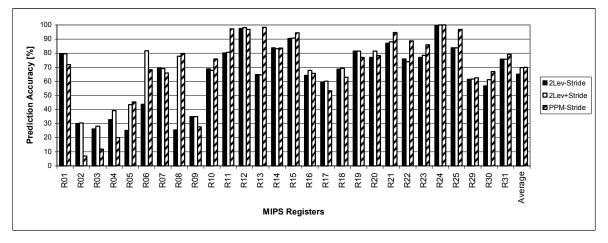

Tot în Capitolul 6 am arătat că există o corelație temporală între numele registrelor și valorile memorate în acestea. De aceea am extins predicția dinamică a valorilor prin introducerea conceptului de predicție a valorilor centrată pe contextul CPU (registre) și nu pe instrucțiuni. Practic se prezice valoarea registrului destinație curent bazat pe analiza valorilor anterioare ale acestuia. Localitățile valorilor obținute pe anumite registre ale arhitecturii MIPS au fost remarcabile conducând la concluzia că predicția valorilor poate fi aplicată cu succes cel puțin centrat pe aceste registre favorabile, prin atașarea câte unui predictor la nivelul acestora. Astfel se reduce semnificativ numărul predictoarelor și scade corespunzător complexitatea și consumul de putere statică/dinamică. Rezultatele evaluărilor au arătat că predictorul hibrid cu prioritizare dinamică, format dintr-un predictor adaptiv pe două niveluri și unul incremental, exploatează cel mai eficient această corelație, depășind chiar și hibridul mult mai complex format dintr-un predictor PPM (Prediction by Partial Matching) și unul incremental.

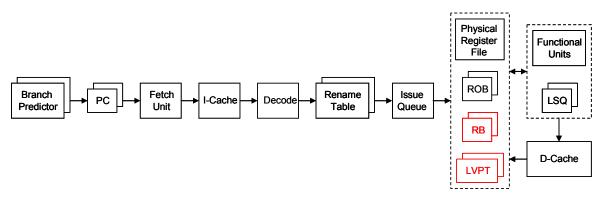

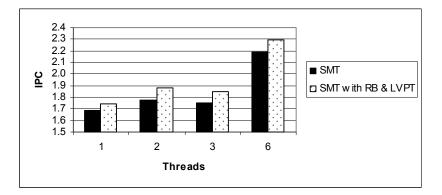

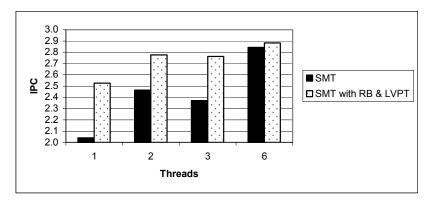

După ce am arătat utilitatea anticipării selective a instrucțiunilor cu latență ridicată într-o arhitectură superscalară, în Capitolul 7 am analizat eficiența acestor metode și într-o arhitectură SMT, focalizându-ne pe aceleași instrucțiuni: Mul și Div respectiv Load-uri critice. Rezultatele au arătat îmbunătățiri IPC pe toate configurațiile SMT evaluate. Cu cât numărul de fire este mai mare, cu atât creșterea de performanță devine însă tot mai puțin semnificativă, datorită exploatării tot mai eficiente a unităților de execuție partajate de către procesorul SMT. Plastic spus, cu motorul SMT mergând în plin, sporul de performanță aferent tehnicilor anticipative implementate adițional devine mai mic. Cele mai bune performanțe medii, de 2,29 IPC pe benchmark-urile de numere întregi respectiv de 2,88 IPC pe cele flotante, s-au obținut cu șase fire de execuție.

În Capitolul 8 sunt trecute succint în revistă contribuțiile științifice ale acestei lucrări și sunt evidențiate câteva dintre direcțiile viitoare de cercetare.

VII

"Lucian Blaga" University of Sibiu "Hermann Oberth" Engineering Faculty Computer Science Department

# Advanced Prediction Methods Integrated Into Speculative Computer Architectures

PhD Thesis

Abstract

Author: Árpád GELLÉRT, MSc

PhD Supervisor: Professor Lucian N. VINŢAN, PhD

PhD Co-supervisor: Professor Theo UNGERER, PhD

SIBIU, 2008

First of all I express my sincere consideration and deep gratitude to my PhD supervisor Professor Lucian VINTAN for his responsible and valuable scientific coordination, for providing stimulating discussions focused on my PhD work and for his generous support. My full recognition to my PhD co-supervisor Professor Theo UNGERER from the University of Augsburg (Germany) for the useful discussions and for all his various support. I express my gratitude to Dr. Adrian FLOREA for his continuous help and his very useful advices. Also my gratitude to Dr. Colin EGAN from the University of Hertfordshire (UK) for his research collaboration. I am also grateful to my colleagues from the Computer Science Department of "Lucian Blaga" University, for their support and for a good working environment assured during my PhD programme. Finally, I would like to thank my family for their patience and for all they have done for me.

This work was supported in part by the Romanian Agency for Academic Research (CNCSIS) through the research grants TD-248/2007-2008 and A-39/2007-2008. It was also partially carried out under the HPC-EUROPA project (RII3-CT-2003-506079), with the support of the European Community – Research Infrastructure Action under the FP6 "Structuring the European Research Area" Programme.

# Contents

| 1. Introduction                                                                                                 | 4                |

|-----------------------------------------------------------------------------------------------------------------|------------------|

| 2. Speculative Computer Architectures                                                                           | 6                |

| 2. Speculative Computer Architectures                                                                           | — <sub>7</sub>   |

| 2.2. The Architecture of Sim-Outorder                                                                           | 9                |

| 3. Finding Difficult-to-Predict Branches                                                                        |                  |

| 3.1. Methodology of Identifying Unbiased Branches                                                               |                  |

| 3.2. Experimental Results                                                                                       |                  |

| 3.2.1. Pattern-Based Correlation                                                                                | $-\frac{13}{15}$ |

| 3.2.2. Path-Based Correlation                                                                                   | 16               |

| 4. Predicting Unbiased Branches                                                                                 |                  |

| 4.1. Value-History-Based Branch Prediction with Markov Models                                                   |                  |

| 4.1.1. Local Branch Difference Predictor                                                                        | 10               |

| 4.1.2. Combined Global-Local Branch Difference Predictor                                                        | 18               |

| 4.1.3. Branch Difference Prediction by Combining Multiple Partial Matches                                       | 19               |

| 4.2. Using Previous Branch Condition as Prediction Information                                                  | 20               |

| 4.2.1. The GAg Predictor Using Global PBC Value                                                                 | _ 20             |

| 4.2.2. The PAg Predictor Using Local PBC Value                                                                  | 21               |

| 4.2.3. The Piecewise Linear Branch Predictor Using PBC Value                                                    |                  |

| <b>4.3. Experimental Results</b> 4.3.1. Evaluating State-of-the-Art Branch Predictors                           | _ 23             |

| 4.3.1. Evaluating State-of-the-Art Branch Predictors                                                            | _ 23             |

| 4.3.2. Evaluating PBC-Based Branch Predictors                                                                   | 24               |

| 5. Better Understanding Unbiased Branches Using Random Degrees                                                  | 25               |

| 5.1. Random Degree Metrics for Characterizing Unbiased Branches Behavior                                        | 25               |

| 5.1.1. Random Degree Metric Based on Hidden Markov Models                                                       | 25               |

| 5.1.2. Random Degree Metric Based on Discrete Entropy                                                           | _ 26             |

| 5.1.3. Random Degree Metric Based on Compression Rate                                                           | 26               |

| 5.1.4. Random Degree Metric Based on Kolmogorov Complexity                                                      |                  |

| 5.2. Evaluation Results                                                                                         | _ 27             |

| 5.2.1. Random Degree Evaluation with HMMs                                                                       | $-\frac{28}{28}$ |

| 5.2.2. Random Degree Evaluation Based on Discrete Entropy                                                       | • •              |

| 5.2.3. Random Degree Evaluation Based on Compression Rate                                                       | $-\frac{29}{30}$ |

|                                                                                                                 | _ 50             |

| 6. <i>Exploiting Selective Instruction Reuse and Value Prediction in a Superscalar</i><br><i>Architecture</i>   | 21               |

|                                                                                                                 | _ 31             |

| 6.1. Anticipating Long-Latency Instructions Results                                                             | $-\frac{31}{32}$ |

| 6.1.1. Selective Dynamic Instruction Reuse                                                                      | $-\frac{32}{33}$ |

|                                                                                                                 |                  |

| 6.1.3. Experimental Results                                                                                     | -36              |

| 6.2.1. Register Value Predictors                                                                                | $-\frac{30}{36}$ |

| 6.2.2. Experimental Results                                                                                     | _ 41             |

| 7. Enhancing the Simultaneous Multithreading Paradigm Through Selective Instruction                             | ı                |

|                                                                                                                 |                  |

| Reuse and Value Prediction           7.1. Selective Instruction Reuse and Value Prediction in SMT Architectures | - <i>11</i>      |

| 7.2. Experimental Results                                                                                       | 45               |

| 8. Conclusions and Further Work                                                                                 |                  |

|                                                                                                                 | - 51             |

| References                                                                                                      | _ 31             |

# **1. Introduction**

The number of instructions that can be processed simultaneously in multiple instruction issue (MII) microprocessors is limited by dependencies existing between instructions. To eliminate these dependencies modern architectures, some of them presented in Chapter 2 as prerequisites for this work, rely heavily on speculation. The main goal of this thesis is to increase instruction-level parallelism (ILP) and therefore the overall performance of superscalar and multithreaded microarchitectures through advanced dynamic anticipatory techniques like branch prediction, value prediction and instruction reuse. This work brings original contributions in identifying difficult-to-predict branches and improving their predictability, in characterizing the randomness of their behavior, and in developing some selectively applied value prediction and instruction reuse methods.

Branch instructions, appearing in high level program constructs like *if, switch, for, while*, etc., are a major bottleneck in the exploitation of ILP, since (in general-purpose code) conditional branches occur approximately every 5 – 8 instructions [Hen03]. Therefore, almost all present-day multiple instruction issue microprocessors are using advanced branch prediction techniques in order to increase ILP. Several prediction methods have been developed based on some well-known learning algorithms (Markovian, neural, Bayesian, decision trees, support vector machine, etc.) simplified for efficient hardware implementation. Through dynamic branch prediction microprocessors are speculatively processing multiple basic blocks in parallel and therefore their ability to increase ILP is stronger. In order to improve performance, branches must be detected within the dynamic instruction stream, and both the direction taken by each branch and the branch target address must be correctly predicted. Furthermore, predictions must be completed in time to fetch instructions from the branch target address without interrupting the flow of new instructions to the processor pipeline [Vin07]. In the case of misprediction, the CPU context must be recovered and the correct paths have to be reissued. As instruction issue width and the pipeline depth of MII processors are getting higher (allowing more aggressive clock rates in order to improve the overall performance), accurate dynamic branch prediction becomes more essential [Spr02]. Very high prediction accuracy is required because an increasing number of instructions are lost before a branch misprediction can be corrected. As an example, the performance of the Pentium 4 equivalent processor degrades by 0.45% per additional misprediction cycle, and therefore the overall performance is very sensitive to branch prediction. Taking into account that the average number of instructions executed per cycle (IPC) grows nonlinearly with the prediction accuracy [Yeh92], it is very important to further increase the accuracy achieved by present-day branch predictors. From a technological point of view, modern high-end processors use quite large tables for branch direction and target prediction [Sez02], and they are accessed every cycle resulting in significant energy consumption, sometimes more than 10% of the total chip power [Cha03]. Therefore, power consumption is another important constraint of all present-day branch predictors.

The quality of a prediction model is highly dependent on the quality of the available data. Especially the choice of the *features* to base the prediction on is important. The vast majority of branch prediction approaches rely on usage of a greater number of input features without taking into account the real causes (indirect jumps and calls and, especially, unbiased branches) that produce a lower accuracy and implicit lower performance. In Chapter 3 we identified difficult-to-predict branches as being unbiased branches that have a "random" dynamic behavior, and tried to improve their predictability through context length extension. In Chapter 4 we showed that present-day branch predictors cannot accurately predict these branches due to their limited prediction information (branch address, local/global branch history, path). Therefore we

improved several state-of-the-art branch predictors with additional prediction information, namely the previous branch condition or even a compressed branch condition history, in order to improve their prediction accuracy. We also showed in Chapter 5 that sequences generated by unbiased branches are characterized by high random degrees.

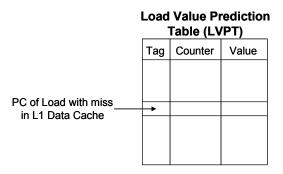

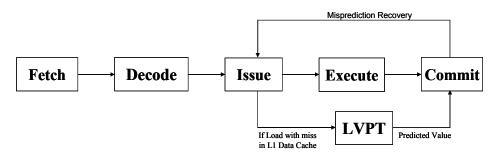

Long-latency instructions, especially critical Loads due to their memory wall problem (the increasing gap between processor and memory speeds), represent another source of ILP limitation. A solution to reduce the number of cache misses consists in prefetching speculatively data from memory to cache. Multithreading can also reduce the effects of the memory wall by hiding memory latency through issuing into the pipelines instructions from different idle threads. Value Prediction (VP) is another technique that increases performance by eliminating true data dependency constraints. VP architectures allow data dependent instructions to issue and execute speculatively using the predicted value. The speculative executions are validated when the correct values are known. If the value was correctly predicted the critical path is reduced, otherwise the instructions executed with wrong entries must be executed again. On the other hand, dynamic instructions with the same input values. The main benefit of reusing long-latency instructions consists in unlocking dependent instructions.

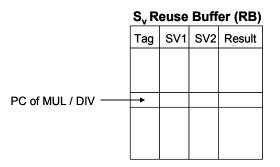

In Chapter 6 we developed a superscalar architecture that selectively anticipates the values produced by long-latency instructions. We focused on Multiply, Division and Loads with miss in the L1 data cache. Thus, we implemented a Dynamic Instruction Reuse scheme for the Mul/Div instructions and a simple Last Value Predictor for the critical Load instructions. We also extended dynamic VP by introducing the concept of register-centric prediction instead of instruction-centric prediction. The register value prediction technique consists in predicting registers' next values based on the previously seen values. It executes the subsequent data dependent instructions using the predicted values. In Chapter 7 we evaluated a simultaneous multithreaded architecture enhanced with selective instruction reuse and value prediction to anticipate the results of long-latency instructions.

Finally, Chapter 8 concludes the thesis pointing out the original contributions and suggests some further work directions.

5

All processors since about 1985 use pipelining in order to improve performance by overlapping the execution of instructions. A pipeline acts like an assembly line with instructions processed in phases. With simple pipelining, only one instruction at a time is introduced into the pipeline, but multiple instructions may be in different phases of execution concurrently. In the case of superscalar processors, more than one instruction at a time can be introduced into multiple pipelines to be executed simultaneously. This potential execution overlap among independent instructions is called instruction-level parallelism (ILP). There are some features of both programs and processors that limit the amount of parallelism such as structural hazards, data hazards and control stalls. In particular, to exploit instruction-level parallelism it must be determined which instructions can be executed simultaneously in a pipeline without causing any stalls, assuming that the pipeline has sufficient resources. If two instructions are dependent they are not parallel and must be executed in order. There are three different types of dependences: data dependences, name dependences and control dependences.

An instruction is data dependent if it uses the result produced by another instruction. Data dependences can be overcome through hardware techniques (dynamic instruction reuse, value prediction) and software techniques (by reorganizing the code). When two dependent instructions are close enough to change the order of access to the operand involved in the dependence, a data hazard occurs. Considering two successive instructions i and j, a RAW (read after write) data hazard occurs when instruction j tries to read a source before i writes it, so j incorrectly gets the old value. A WAW (write after write) data hazard occurs when instruction j tries to write an operand before it is written by i. A WAR (write after read) data hazard occurs when instruction j tries to write a destination before it is read by i.

Name dependences occur when two instructions use the same register or memory location. Instructions involved in name dependence can be executed simultaneously or reordered if the register or memory location used by the instructions is changed so the instructions do not conflict. This renaming can be more easily done for register operands (register renaming), either statically by a compiler or dynamically by the hardware.

Control dependences are generated by branch instructions. An instruction that is control dependent on a branch cannot be executed until the branch direction is known. Control stalls can be eliminated or reduced by a variety of hardware techniques (branch prediction) and software techniques (static scheduling).

A major limitation of the simple pipelining techniques is that they all use in-order instruction issue and execution. Instructions are issued in program order and if an instruction is stalled in the pipeline, no later instructions can proceed. Out-of-order execution introduces the possibility of data hazards. Hennessy and Patterson in [Hen03] explore an important technique, called dynamic scheduling, in which the hardware rearranges the instruction execution in order to reduce the stalls. In a dynamically scheduled pipeline, all instructions are dispatched in order, however, they can be stalled or bypass each other in the *issue* stage and thus execute out of order.

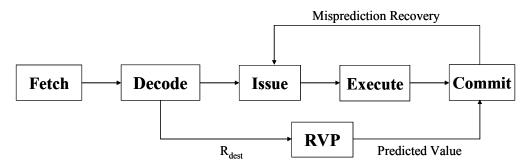

Branch prediction is a mechanism that reduces control stalls in order to improve performance in a multiple instruction issue processor. Control dependences are overcome by speculating on branch outcomes and executing dependent instructions as if the predictions were correct. Obviously it became necessary the integration of branch prediction into dynamically scheduled processors. Predicting the outcomes of conditional branches, more instructions can be fetched in parallel (a part of them are fetched speculatively from the predicted path), increasing in this way the execution window [Smi95]. The fetched instructions are analyzed for true data dependences, issued to the functional units and executed out-of-order, in parallel, based on the availability of the operands. Value prediction is another technique that speculatively forwards predicted instruction results to the dependent instructions. With speculative execution, the architectural storage cannot be updated immediately when instructions complete execution. The results must be held in a temporary status until the architectural state can be updated in sequential program order.

#### 2.1. Speculative Dynamic Scheduling with Reorder Buffer

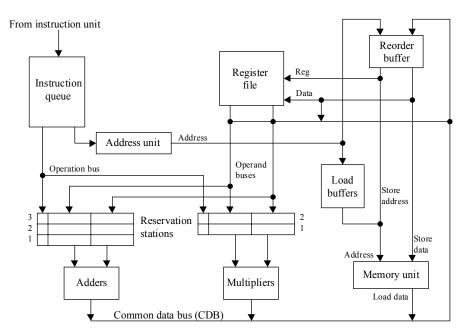

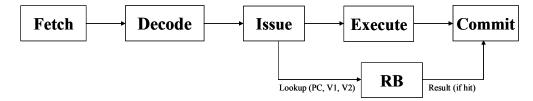

The present-day out-of-order issue superscalar microprocessor model is implemented as a speculative microarchitecture that actually fetches, issues and executes instructions based on branch prediction using Tomasulo's algorithm or closely related algorithms and a structure called *Reorder Buffer* (ROB). Figure 2.1 shows the hardware structure of the processor including the ROB.

Figure 2.1. Tomasulo's architecture extended to support speculation

The hardware that implements Tomasulo's algorithm [Tom67] can be extended to support speculation, only if the bypassing of results, which is needed to execute an instruction speculatively, is separated from the completion of an instruction (that consists in updating the memory or register file). Doing this separation, an instruction bypasses its results to other instructions, without performing any CPU updates that cannot be canceled. When the instruction is no longer speculative (after its *writeback* stage), it updates the register file or memory; this phase is called instruction *commit*. Separating the bypassing of results from instruction completion makes possible avoiding imprecise exceptions in out-of-order execution, preserving in this way exception behavior. An exception is imprecise if the processor state when the exception raised is not exactly as in the case of sequential execution.

Adding this *commit* phase to the instruction execution sequence, an additional set of hardware buffers is required, which hold the results of instructions that have finished execution but have not yet committed. The reorder buffer provides the register renaming function and it is also used to pass the results of speculatively executed instructions. The reservation stations keep operations and operands only between the time they issue end the time they begin execution.

Each ROB entry contains four fields: *Type*, *Dest*, *Value* and the *Ready* field. The *Type* field indicates whether the instruction is a branch, a Store, or a register operation (ALU operation or Load). The *Dest* field supplies the register number for Loads and ALU operations or the memory address for Stores, where the instruction result must be written. The *Value* field is used to hold the value of the result until the instruction commits. The *Ready* field indicates if the instruction has completed execution and the value is ready. The ROB completely replaces the Store buffers. The ROB is usually implemented as a circular FIFO queue having associative search facilities.

Each reservation station has the following eight fields:

- *Op* the operation performed on the source operands (*opcode*);

- $Q_j$ ,  $Q_k$  the ROB entries that will provide the source operands, a value of zero indicating that the source operand is already available in V<sub>j</sub>, V<sub>k</sub>, or that it is unnecessary;

- $V_j$ ,  $V_k$  the values of the source operands; for Loads and Stores the V<sub>j</sub> field is used to hold the offset;

- *A* holds the memory address for Loads or Stores: initially holds the immediate field, after the address calculation holds the effective address;

- *Dest* supply the corresponding ROB entry number representing the destination for the result produced by the execution unit.

- Busy indicates if a reservation station is available or occupied.

The register file has a field  $Q_i$  indicating the number of the ROB entry that contains the operation whose result should be stored into the register. The six steps involved in instruction execution are the following [Hen03]:

- 1. Fetch fetches the next instruction into the instruction queue.

- 2. Dispatch gets the next instruction from the instruction queue. If all reservation stations are full or the ROB is full, then instruction dispatch is stalled until both structures have available entries. If there is an empty reservation station and the tail of the ROB is free, the instruction is sent to the reservation station. The *Busy* bit of the allocated reservation station is set and the *Ready* field of the ROB entry is reset. The source registers are searched associatively in the *Dest* field of the ROB, considering the last entry in the case of multiple hits, since the ROB entries are allocated in order. If an operand value is available in the ROB (*Ready=1*), it is written from the *Value* field into the reservation station field  $V_j / V_k$ . If the operand value is not available (*Ready=0*), the number of ROB entry that will provide the operand is written into the register set into the reservation station field  $V_j / V_k$ . The number of ROB entry allocated for the value of the result is sent into the *Dest* field of the reservation station. The destination register number is written into the *Dest* field of the reservation station.

- 3. *Issue* if an operand is not yet available, the common data bus (CDB) is monitored until it is computed and when the operand is available on the CDB it is placed into the corresponding reservation stations. In order to avoid structural hazards, modern processors have multiple CDBs and a multiported ROB. When all the operands are available, the instruction is issued to the appropriate functional unit. By delaying instruction execution until the operands are available, RAW dependences are detected.

- 4. *Execute* the corresponding functional unit executes the operation. In the case of Loads and Stores the effective memory address is computed in this stage. In the case of a taken branch, usually is calculated the branch's target address.

- 5. *Writeback* when the result is available, it is written to the CDB (together with the ROB entry number indicated by the *Dest* field of the reservation station) and from there into the *Value* field of the corresponding ROB entry, whose *Ready* field is set to 1. The *Busy* field of the corresponding reservation station is reset. The result is also written into field  $V_j / V_k$  of the

reservation stations that are waiting for it. In the case of a Store instruction if the value to be stored is available, it is written into the *Value* field of the ROB entry allocated for that Store. If the value to be stored is not available, the CDB is monitored, and when it is received, the *Value* field of the ROB entry is updated.

6. *Commit* – the normal *commit* case occurs when an instruction reaches the head of ROB having its result available (*Ready*=1) and if no exception occurs. In this case, the result is written from the *Val* field of the ROB entry into the destination register or memory location indicated by the *Dest* field of the ROB entry and, after that, the instruction is squashed from the ROB. Thus, the in order *commit* is guaranteed by the in order *dispatch*, whereas the *issue*, *execute* and *writeback* stages can be processed out of order. When an incorrectly predicted branch reaches the head of the ROB, the ROB is flushed and the execution is restarted with the correct successor of the branch.

As it can be observed, in the case of speculative architectures is very important *when* is performed the updating. Using the ROB, speculative executions are possible because the register file or memory is updated with the result of an instruction only when that instruction is no longer speculative.

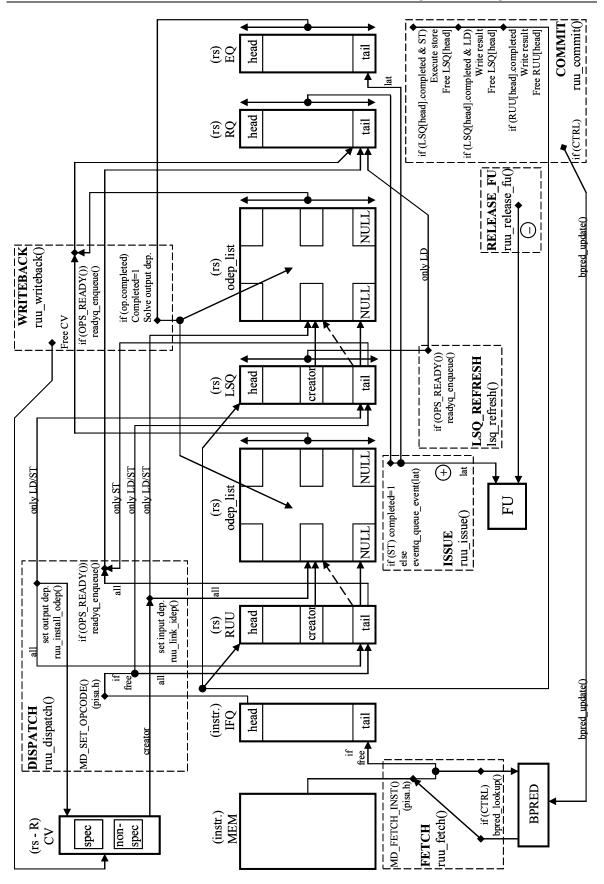

# 2.2. The Architecture of Sim-Outorder

In this work we relied on some commonly used simulators like *Simplesim* [Bur97] and the *M*-*SIM* [Sha05] which extends the *Simplesim* toolset with support for concurrent execution of multiple threads and power consumption evaluation. The *sim-outorder* simulator (see Figure 2.2) from the *Simplesim-3.0* toolset [Bur97] simulates a superscalar architecture that uses a register update unit (RUU) in order to support out-of-order and speculative execution. The RUU is a combination of reservation stations and ROB, and is organized as a circular queue. Each RUU entry contains the following fields:

- *IR* stores the instruction bits.

- *op* holds the opcode after the instruction is decoded in the *dispatch* stage.

- *PC* the instruction address.

- *next* PC the next instruction address.

- *pred PC* the next predicted instruction address.

- *ea\_comp* non-zero if the operation is an address computation (the first operation in the case of Load and Store instruction preceding the memory access).

- *in\_LSQ* non-zero if the Load/Store operation is in the LSQ.

- *recover inst* indicates when an instruction is the start of misspeculation.

- *dir\_update* pointer to the branch predictor state entry.

- *spec mode* indicates if the instruction was fetched speculatively.

- *addr* holds the effective address for Load/Store instructions.

- *tag* RUU slot tag, used to identify an operation in the RUU.

- *queued* indicates that the operands are ready and the operation was queued to the *ready\_queue*.

- *issued* indicates that the operation was issued for execution.

- *completed* indicates that the operation has completed the execution.

- *onames* output logical register names.

- *odep\_list* dependency list containing a pointer to all dependent RUU entries. These lists are used to limit the number of associative searches in the RUU when operations complete the execution and need to wake up dependent operations.

- *idep\_ready* indicates if the input operands are ready.

Figure 2.2. The architecture of Sim-Outorder

For Loads and Stores a Load/Store Queue (LSQ) is also used. The LSQ has the same structure as the RUU. Load and Store instructions are split in two operations: the effective address computation that is inserted into the RUU and the Load/Store operation that is inserted into the LSQ and is activated by the RUU when the address computation is finished. A renametable structure called Create Vector (CV) holds for each register the last mapped RUU or LSQ entry that will write the result into that register. The CV is divided into a speculative table (maintains the last speculative state of the register file) and a non-speculative table (maintains the last non-speculative state of the register file). The CV is used to handle instruction dependencies: to construct the dependency lists (*odep list*) and to squash efficiently the RUU and LSQ structures if an exception occurs. An instruction fetch queue (IFQ) is used to hold the instructions fetched from memory. Each IFQ entry has the following fields: IR (holds instruction bits), regs PC (instruction address), pred PC (next predicted instruction address) and *dir update* (pointer to the branch predictor state entry). A ready queue (RO) is used to hold operations whose operands are ready and an event queue (EQ) holds operations during their execution. Each RQ and EQ location contains only a pointer to the RUU or LSQ entry associated to the operation.

The *sim-outorder* simulator uses a pipeline with five important stages implemented in software: *fetch, dispatch, issue, write back* and *commit.* The classical execution stage is distributed into the *dispatch* and *issue* stages as we will detail further. In the software implementation of this superscalar architecture the pipeline stages are executed sequentially and are not overlapped leading in this way to synchronization problems. More exactly, because one cycle of execution in the simulator corresponds to the sequential iteration of all pipeline stages once, the effects of a certain stage are "instantaneously" seen by the next pipeline stages too early, in the current cycle, while they must be seen only in the next cycle. Therefore, in order to eliminate these synchronization problems, the pipeline stages are traversed in reverse order, and thus, the effects of a certain one-cycle operation are visible correctly only in the next cycle (iteration). The seven execution steps of *sim-outorder* are the following:

- 1. Fetch (ruu\_fetch) as many instructions are fetched up (MD\_FETCH\_INST) as one branch prediction and one instruction-cache line support, without overflowing the instruction fetch queue (IFQ). The instructions are inserted into the tail of the IFQ (fetch\_data). If the simulator is started with a branch predictor, the instructions are pre-decoded in order to identify branches (MD\_SET\_OPCODE). When a branch instruction occurs the next instruction is fetched from the address pred\_PC predicted using a certain pred branch predictor (bpred lookup).

- 2. Dispatch (ruu dispatch) gets the next instruction from the head of the IFQ, decodes the instruction (MD SET OPCODE), and inserts it into the tail of the RUU if it is free. For Loads and Stores the effective address computation is inserted into the tail of the RUU, and the Load/Store operation is inserted into the tail of the LSQ. If the RUU/LSQ is full, then instruction dispatch is stalled until the structure has available entries. The dispatched instructions are removed from the IFQ. A pointer to the allocated RUU/LSQ entry (rs) is introduced into the dependency list (odep list) corresponding to the RUU/LSQ entries identified based on the CV – that will produce the input operands (ruu link idep). The output register numbers are written into the onames field and a pointer to the allocated RUU/LSQ entry (rs) is set to all the output registers in the CV structure (ruu install odep). If all the input operands are available, a pointer to the allocated RUU/LSQ entry (rs) is inserted into the tail of the RQ (readyg enqueue). Actually the simulator "instantaneously" executes the operation in this stage, but correctly simulates its latency through the write-back event in the next stages. In the case of a Store instruction a pointer to the allocated LSQ entry is also inserted into the tail of the RQ (Load operations are queued into the RQ only in the LSQ-refresh stage).

- 3. Issue (ruu\_issue) tries to issue all instructions from the RQ (ready\_queue) to free functional units (FU) whose busy count is set to the latency value corresponding to the issued operation. A writeback-event is scheduled for each issued operation to the cycle obtained adding its execution latency to the current cycle: a pointer to the corresponding RUU/LSQ entry (rs) is inserted together with the scheduled writeback-cycle (wb\_cycle) into the EQ (event\_queue\_event). The EQ (event\_queue) is sorted from earliest to latest event. The issued operations are evacuated from the RQ. The issue stage ends with the execution of the operations at the functional units (the previously presented Tomasulo's architecture has an additional execute stage for this operation). Thus, the execution is simulated by scheduling the writeback-event to the cycle obtained by adding the corresponding execution latency to the current cycle. Store operations are executed only in the commit stage.

- 4. LSQ-refresh (lsq\_refresh) a pointer to each Load operation (rs) from the LSQ whose operands are ready is inserted into the RQ (readyq\_enqueue). Store operations are inserted during the dispatch stage.

- 5. Writeback (ruu\_writeback) in the case of a misprediction the RUU/LSQ entries corresponding to speculatively fetched instructions are squashed and the CV is reverted to the last non-speculative state. In the normal writeback case, for each event from the EQ whose scheduled writeback-cycle is less than or equal to the current execution cycle (the event has already occurred), the result is written from the functional unit (FU) to the RUU/LSQ, and the event is removed from the EQ. If the RUU/LSQ entry afferent to the completed operation is still mapped in the CV to the output registers, the corresponding CV entries are invalidated (assigning NULL), because the construction of the operation's dependency list (odep\_list) finished. Dependent operations that occur in the future will get the result from the RUU/LSQ or from the register file. Each RUU/LSQ entry that has a pointer in the dependency list (odep\_list) of the completed operation is updated with the result, and if all its operands are ready, it is queued into the RQ its pointer (rs) is inserted into the tail of the RQ (readyq\_enqueue).

- 6. *FU-release* (*ruu\_release\_fu*) the *busy* count of each FU is decremented by 1. An FU is free for another operation when its *busy* count is 0.

- 7. Commit (ruu\_commit) the normal commit case occurs when an instruction reaches the head of the RUU/LSQ and its result is available (completed=TRUE). The results are written from the head of the RUU/LSQ into the register file. If a Store instruction occurs in the head of the LSQ, the Store data is written to the data cache. At the end of the commit stage the head of the RUU/LSQ is freed and, in the case of branch instructions, the used branch predictor pred is updated (bpred\_update).

The *fetch*, *dispatch* and *commit* stages are effectuated in program order avoiding thus imprecise exceptions, while the other stages might be executed out of order. In fact, instruction execution is done "instantaneously" in *ruu\_dispatch*. Thus, instructions flow down the pipeline only for timing evaluations. Therefore, there is no need to actually store the result value into the RUU/LSQ structure at the end of the *writeback* stage and there is no need to update the register file in the *commit* stage because that's already been done in the *dispatch* stage.

Since the performances of modern speculative architectures highly depend on branch prediction accuracy, we will further focalize on some branch prediction limitations, namely, on hard-topredict branches. Our first goal is to identify difficult branches in the SPEC 2000 benchmarks [SPEC]. We consider that a branch in a certain context is difficult-to-predict if it is unbiased (the branch behavior is not sufficiently polarized for that certain context) and the taken and not taken outcomes are non-deterministically shuffled. The second goal is to improve prediction accuracy for branches with low polarization rate, introducing new feature sets that will increase their polarization rate and, therefore, their predictability.

# 3.1. Methodology of Identifying Unbiased Branches

Based on our previous work already published in [Gel06a, Vin06, Oan06, Gel07c] we are presenting in this paragraph the methodology of finding difficult-to-predict branches, as they are defined in our approach. For each processed dynamic branch, the prediction is achieved based on some binary context information (local or global branch history, the path leading up to the branch, etc.). We have statistically observed that some dynamic branches occurring in certain contexts have a highly unbiased behavior. We consider that a branch in a context is difficult-to-predict if it is unbiased and the taken and not taken outcomes are shuffled. Therefore, we evaluate the impact of unbiased branches on different commonly used features.

We called feature the binary context on p bits of prediction information such as local history, global history or path. Each static branch finally has associated k dynamic contexts in which it can appear ( $k \le 2^p$ ). A context instance is a dynamic branch executed in the respective context. We introduce the polarization index (P) of a certain branch context as follows:

$$P(S_i) = \max(f_0, f_1) = \begin{cases} f_0, & f_0 \ge 0.5\\ f_1, & f_0 < 0.5 \end{cases}$$

(3.1)

where:

- $S = \{S_1, S_2, ..., S_k\}$  = set of distinct contexts that appear during all branch instances;

- k = number of distinct contexts,  $k \le 2^p$ , where p is the length of the binary context;

- $f_0 = \frac{T}{T + NT}$ ,  $f_1 = \frac{NT}{T + NT}$ , NT = number of *not taken* branch instances corresponding to context  $S_i$ , T = number of *taken* branch instances corresponding to context  $S_i$ ,  $(\forall)i = 1, 2, ..., k$ , and obviously  $f_0 + f_1 = 1$ ;

- if  $P(S_i) = 1, (\forall)i = 1, 2, ..., k$ , then the context  $S_i$  is completely biased (100%), and thus, the afferent branch is highly predictable;

- if  $P(S_i) = 0.5$ ,  $(\forall)i = 1, 2, ..., k$ , then the context  $S_i$  is totally unbiased, and thus, the afferent branch might be not predictable if the *taken* and *not taken* outcomes are shuffled.

If the *taken* and *not taken* outcomes are grouped separately, even in the case of a low polarization index, the branch is predictable. The unbiased branches are not predictable only if the *taken* and *not taken* outcomes are chaotically shuffled, because in this case, the predictors cannot learn their behavior. We introduce the distribution index (shuffle degree) for a certain branch context, defined as follows:

$$D(S_{i}) = \begin{cases} 0, \ n_{t} = 0 \\ \frac{n_{t}}{2 \cdot \min(NT, T)}, \ n_{t} > 0 \end{cases}$$

(3.2)

where:

- $n_t$  = the number of branch outcome transitions ( $0 \rightarrow 1$  or  $1 \rightarrow 0$ ) in a certain context  $S_i$ ;

- $2 \cdot \min(NT, T) = \max(NT, T)$  = maximum number of possible transitions;

- k = number of distinct contexts,  $k \le 2^p$ , where p is the length of the binary context;

- if  $D(S_i) \rightarrow 1$ ,  $(\forall)i = 1, 2, ..., k$ , then the behavior of the branch in context  $S_i$  is "contradictory";

- if  $D(S_i) \rightarrow 0$ ,  $(\forall)i = 1, 2, ..., k$ , then the behavior of the branch in context  $S_i$  is constant.

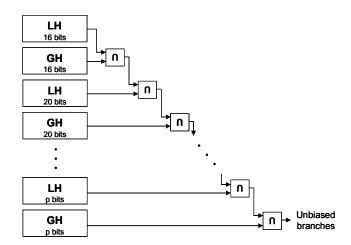

As it can be observed in Figure 3.1, we want to systematically analyze different feature sets used by different present-day branch predictors in order to find and, hopefully, to reduce the list of unbiased branch contexts (contexts with low polarization *P*).

Figure 3.1. Reducing the number of unbiased branches through feature set extension

We approached an iterative methodology: we evaluate and reduce the number of unbiased branches by passing them through successive cascades of different prediction contexts (feature sets). Gradually this list is shortened by increasing the lengths of feature sets (from 16 to 28 bits) and reapplying the algorithm. Thus, the final list of unbiased branches contains only the branches that were unbiased throughout all their contexts, being therefore identified as difficult-to predict. For the final list of unbiased branches we will try to find new relevant feature sets in order to further improve their polarization index and, therefore, the prediction accuracy.

In our experiments we concentrated only on benchmarks with a percentage of unbiased branch context instances (obtained with relation (3.3)), greater than a certain threshold (T=1%) considering that the potential prediction accuracy improvement is not significant in the case of benchmarks with percentage of unbiased context instances less than 1%. If the percentage of unbiased branch contexts is 1%, even if they would be solved, the prediction accuracy would increase with maximum 1%. This maximum can be reached when the predictor solves all discovered difficult-to-predict branches.

$$T = \frac{NUB_i}{NB_i} = 0.01 \tag{3.3}$$

where  $NUB_i$  is the total number of unbiased branch context instances on benchmark *i*, and  $NB_i$  is the number of dynamic branches on benchmark *i* (the total number of branch context instances).

# **3.2. Experimental Results**

### **3.2.1.** Pattern-Based Correlation

In order to reduce the number of unbiased branches, we first increased the lengths of the branch contexts (local/global histories, etc.). We identified and decreased the number of unbiased branches in the SPEC 2000 benchmark suite [SPEC] by passing unbiased branches through successive cascades of different prediction contexts – local history (LH) and global history (GH) – by increasing history information (from 16 to 28 bits).

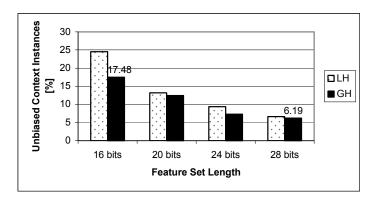

**Figure 3.2.** Reduction of average percentages of unbiased context instances (P<0.95) in the SPEC 2000 benchmarks by extending the lengths of feature sets

Using a global history context of 16 bits, about 17% of branches are unbiased and unpredictable. This number decreases to about 6% if the context has 28 bits. We consider that this value of 6% is still too high and further investigations are required. The evaluation results also show that the "ultimate predictability limit" of history context-based prediction is about 94%, considering unbiased branches as completely unpredictable. A conclusion based on our simulation results is that about 94% of dynamic branches can be solved with prediction information of up to 28 bits.

For the determined unbiased branch contexts we are analyzing now if the *taken* and *not taken* outcomes are grouped separately. This is necessary, because if the branch outcomes are not shuffled they are predictable using corresponding two-level adaptive predictors, but if these outputs are shuffled the branches are not predictable. We used relation (3.2) in order to determine the distribution indexes for each unpredictable branch context per benchmark. We evaluated only the unbiased dynamic branches obtained using all their contexts of 16 bits. As our evaluations show, in the case of unbiased branch contexts, the *taken* and *not taken* outcomes are not grouped separately, more, they are highly shuffled.

The percentage of unbiased branch contexts having highly shuffled outcomes (with distribution index greater than 0.4) is 76.3% in the case of local history of 16 bits and 89.37% in the case of global history of 16 bits. A distribution index of 1.0 means the highest possible alternation frequency (with taken or not taken periods of 1). A distribution index of 0.5 means again a high alternation, since, supposing a constant frequency, the taken or not taken periods are only 2, lower than the predictors' learning times. In the same manner, periods of 3 introduce a distribution of about 0.25, and periods of 5 generate a distribution index of 0.15, therefore we considered that if the distribution index is lower than 0.2 the taken and not taken outcomes are not highly shuffled, and the branch's behavior could be learned.

Taking into account that increasing the prediction accuracy with 1%, the IPC (instructionsper-cycle) is improved with more than 1% (it grows non-linearly) [Yeh92], there are great chances to obtain considerably better overall performances even if not all of the 6.19% difficult predictable branches, from the SPEC 2000 benchmarks, will be solved. Therefore, we consider that this 6.19% represents a significant percentage of unbiased branch context instances, and in the same time a good improvement potential in terms of prediction accuracy and IPC. Focalising on these unbiased branches – in order to design some efficient path-based predictors for them [Nair95, Vin99b] – the overall prediction accuracy should increase with some percents, that would be quite remarkable. The simulation results also lead to the conclusion that as higher is the feature set length used in the prediction process, as higher is the branch polarization index and hopefully the prediction accuracy (Figure 3.2). A certain large context (e.g. 100 bits) – due to its better precision – has lower occurrence probability than a smaller one, and higher dispersion capabilities (the dispersion grows exponentially). Thus, very large contexts can significantly improve the branch polarization and the prediction accuracy, too. However, they are not always feasable for hardware implementation. The question is: what feature set length is really feasable for hardware implementation, and more important, in this case, which is the solution regarding the unbiased branches? In our opinion, as we'll further show, a feasable solution in this case could be given by path-based predictors.

#### **3.2.2.** Path-Based Correlation

The path information could be a solution for relatively short history contexts (low correlations). Our hypothesis is that short contexts used together with path information should replace significantly longer contexts, providing the same prediction accuracy. A common criticism for most of the present two-level adaptive branch prediction schemes consists in the fact that they used insufficient global correlation information [Vin99b]. There are situations when a certain static branch, in the same global history context pattern, has different behaviors (taken / not taken), and therefore the branch in that context is unbiased. If each bit belonging to the global history will be associated during the prediction process with its corresponding PC, the context of the current branch becomes more precise, and therefore its prediction accuracy could be better. Our next goal is to extend the correlation information in this way, suggests that at different occurrences of a certain static branch with the same global history context, the path contexts can be different.

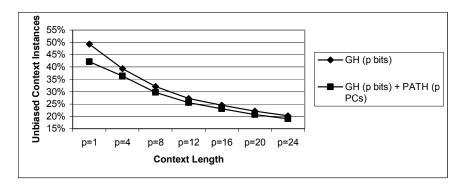

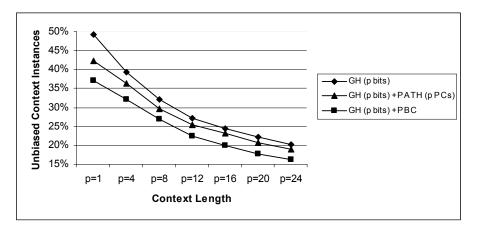

We evaluated – on all branches (non-iterative simulation) – the number of unbiased context instances (P<0.95) using as prediction information paths of different lengths (p PCs) together with global histories of the same lengths (p bits). The results are presented in Figure 3.3 where they are compared with the results obtained using only global history.

Figure 3.3. The gain introduced by the path for different context lengths – SPEC 2000 benchmarks

Figure 3.3 shows that the path is relevant for better polarization rate and prediction accuracy only in the case of short contexts and there is only marginal gain with longer history lengths (p bits), meaning that a global branch history of more than 12 bits approximates very well the longer path information (p PCs).

In Chapter 3 we showed that the percentages of difficult branches are quite significant (at average between 6% and 24%, depending on the different used prediction contexts and their lengths). This chapter presents some important present-day branch predictors and some condition-history-based branch predictors proposed by us in [Gel07a, Gel07b, Gel07c], all of them being used to evaluate, in terms of prediction accuracy, the unbiased branches identified in Chapter 3.

# 4.1. Value-History-Based Branch Prediction with Markov Models

Value predictors that implement the "*Prediction by Partial Matching*" algorithm (PPM) [Saz97, Jos97] represent an important class of context-based predictors. Mudge et al. [Mud96] demonstrates that all two-level adaptive predictors implement special cases of the PPM algorithm that is widely used in data compression. It seems that PPM provides the ultimate predictability limit of two-level predictors. The PPM-based predictor contains a set of simple Markov predictors, each one predicting the value that followed the corresponding context with the highest frequency. In a complete-PPM predictor, if a prediction cannot be furnished by the Markov predictor of order k, then the pattern length is shortened and the Markov predictor of order k-1 is used to furnish the prediction and so on until either a prediction is furnished or the Markov predictor is of the order 0.

Our second idea in order to reduce the number of unbiased branches, after the feature set length extension (presented in Chapter 3), was to find new relevant information that could reduce their entropy making them more predictable. Representing the problem in a superior feature space dimension is a general well-known method in solving many Computer Science classification/prediction problems. Therefore, we predict the condition of the current branch (B<sub>0</sub>) based on the conditions of the previous branches (B<sub>1</sub>, B<sub>2</sub>, ..., B<sub>h</sub>), with different PPM predictors. We use each branch condition as the value or the sign of the difference between the operand values (two approaches). Regarding the approach that uses only the signs of the input differences, a value of 1 indicates that the corresponding branch difference is positive, a -1 indicates a negative difference, while a 0 indicates equality between the branch inputs. The outcome of the current branch B<sub>0</sub> is determined speculatively based on its predicted condition (difference).

But is it better to use only the signs of differences as history information instead of the values of differences? Is this compressed branch condition history more efficient than the most complete value history? The number of distinct symbols that can occur in a value history is huge reported to only three symbols that can appear in a sign history. Thus, the frequency of symbols in a value history is very low. In the following example only a Markov predictor of order 1 can be used for the value history, and it generates a misprediction, while in the case of the sign history, even a Markov predictor of order 5 can be used, which achieves the correct prediction:

```

Value history: -126, -34, 7, -42, -28, 75, -829, -7982, 102, -542, -42, ? Sign history: -1, -1, 1, -1, 1, -1, 1, -1, -1, ?

```

Obviously, through a sign history much deeper correlations can be exploited than with a value history. A natural question is: are the sign histories better than the simplest branch outcome histories (taken / not taken)? The difference-sign history can be more efficient because, due to its

additional information, it can efficiently exploit shorter contexts, too. The following example presents the situation for *bgez*:

If after "0" statistically follows "-" (and, in the case of *bgez*, "0" is associated together with "+" to *taken*) a first order Markov can correctly predict in the case of sign history, while, in the case of outcome history, the Markov predictor must be of order 4 or higher for correct prediction. Anyway, the simulation results will decide which type of branch condition history is the most efficient.

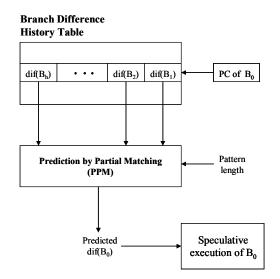

### 4.1.1. Local Branch Difference Predictor

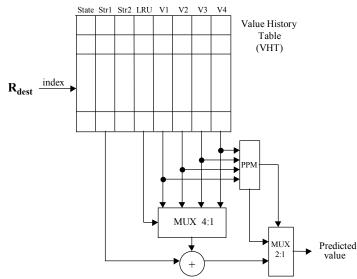

Figure 4.1 presents the speculative branch execution mechanism of our local PPM branchdifference predictor. The Branch Difference History Table (BDHT) maintains for each static branch the differences corresponding to the branch's last *h* dynamic instances (B<sub>1</sub>, B<sub>2</sub>, ..., B<sub>h</sub>). The BDHT entry is selected by the branch address (PC of B<sub>0</sub>). The branch differences from the selected BDHT entry are then used as inputs into the complete-PPM predictor. The PPM predictor of order *k* (where k < h) furnishes the predicted difference of the branch undergoing execution (B<sub>0</sub>). Speculative execution of the branch B<sub>0</sub> based on its predicted difference only occures in the case that the considered pattern of length *k* is repeated in the string of last *h* differences with a frequency greater than or equal to a certain threshold value.

Figure 4.1. A local PPM-based branch-difference predictor

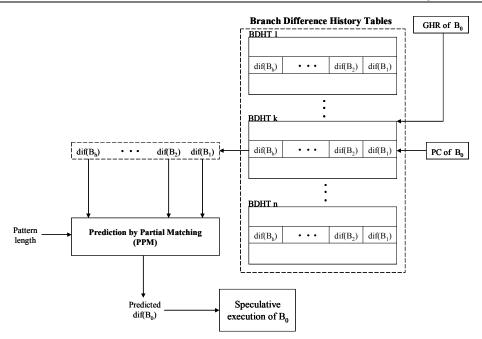

#### 4.1.2. Combined Global-Local Branch Difference Predictor

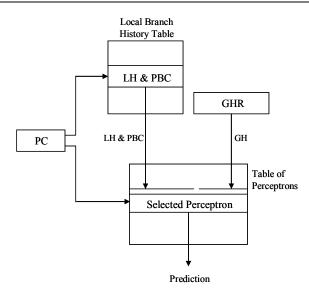

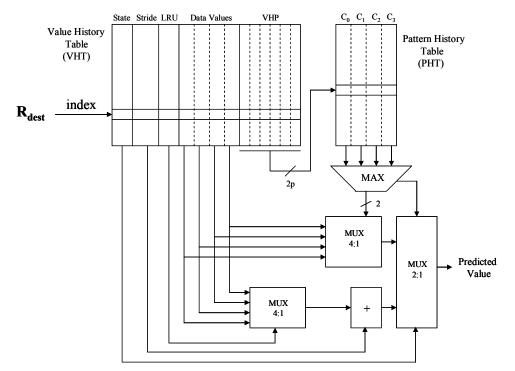

Figure 4.2 presents the speculative branch execution mechanism using a combined global and local PPM-based branch-difference predictor. The Global History Register (GHR) contains the global history: the global branch difference history or the global branch outcome history (two different approaches). For each global history pattern, a distinct BDHT is maintained. Thus, the BDHT is selected by the GHR. Each BDHT is configured as a local BDHT and is accessed as described in section 4.1.1.

Figure 4.2. A global-local PPM-based branch-difference predictor

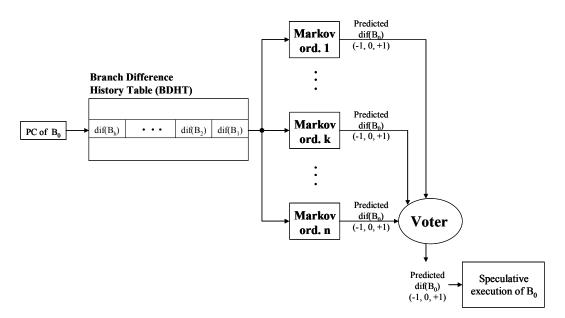

#### 4.1.3. Branch Difference Prediction by Combining Multiple Partial Matches

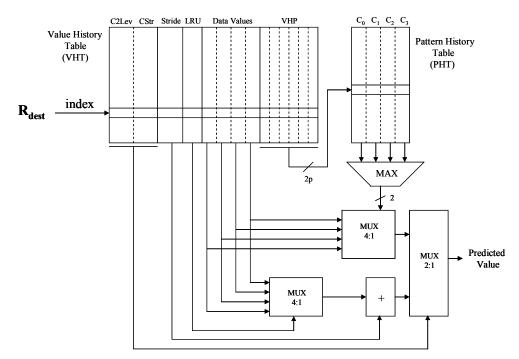

Figure 4.3 presents the speculative branch execution mechanism using the *Branch-Difference Predicion by Combining Multiple Partial Matches* (BPCMP). An entry in the BDHT is accessed as described in section 4.1.1, but now the *h* branch differences are used as inputs into multiple Markov predictors of different orders. Thus, the sign of the input difference (-1, 1, or 0) corresponding to the current branch (B<sub>0</sub>) is predicted using multiple Markov predictors of orders ranging between [1, *n*], n < h (see Figure 4.3). The final branch difference prediction is then furnished through majority vote.

Figure 4.3. Branch-difference prediction by combining multiple Markov predictors

We have also investigated a confidence-based voting mechanism. In this case, each BDHT entry holds *n* saturated confidence counters, in the range [-4, 4], which are associated with the *n* Markov predictors. A certain Markov predictor of order k ( $1 \le k \le n$ ) will furnish a value prediction if the corresponding pattern occures at least once in the history of *h* values. In the case of a correctly predicted branch, its confidence saturating counter is incremented and decremented in the case of a misprediction. Each Markov prediction is replicated as many times as the corresponding counter's value shows (only if this value is greater than zero). These multiple predictions are then passed to the voter, which furnishes the most frequent value.

## 4.2. Using Previous Branch Condition as Prediction Information

In this section we tried to use the value of previous branch condition (PBC) as prediction information, taking into account that it determines branch's behavior. A PBC value consists in the difference of the operand values involved in the previous branch condition. Using only one branch condition is in concordance with Heil's observation in [Hei99b] that majority of prediction accuracy improvement is gained by using a single branch difference. First we evaluated the percentage of unbiased context instances (having polarization *P* less than 0.95) using the PBC value together with the global histories of *p* bits ( $1 \le p \le 24$ ). Figure 4.4 compares the percentages of unbiased branches using the global history (GH), the global history concatenated with the path (GH + PATH), and the global history concatenated with the value of the previous branch condition (GH + PBC).

Figure 4.4. The gain introduced by the previous branch condition (PBC) vs. the path for different context lengths – SPEC 2000 benchmarks

The experimental results, presented in Figure 4.4, show that the PBC value is more efficient than the path information: it decreased the percentage of unbiased branches for all evaluated context lengths ( $1 \le p \le 24$ ). Therefore we could use this new prediction information in some state-of-the-art branch predictors in order to increase prediction accuracy [Gel07a, Gel07b, Gel07c].

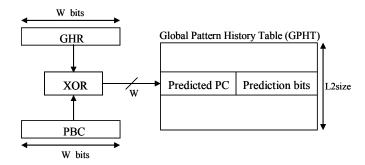

#### 4.2.1. The GAg Predictor Using Global PBC Value

We first analyzed a GAg scheme that uses the previous branch condition (PBC) by XORing it with the GHR (as the Gshare XORed the PC with the GHR). The predictor's scheme is presented in Figure 4.5.

Figure 4.5. The GAg predictor using the previous branch condition (PBC)

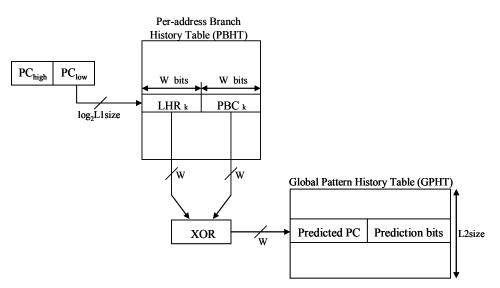

## 4.2.2. The PAg Predictor Using Local PBC Value

We have also analyzed a PAg scheme that uses the local (per-address) PBC value (previous branch condition) by XORing it with the LHR (local history register). The Per-address Branch History Table (PBHT) maintains for each branch its own Local History (LH) and its Previous Branch Condition (PBC) value. The predictor is presented in Figure 4.6.

Figure 4.6. The PAg predictor using the local PBC value

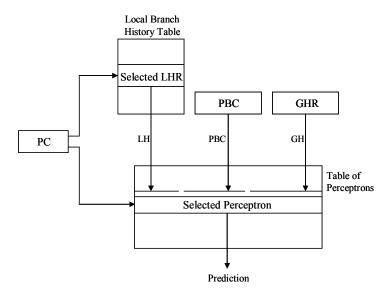

#### 4.2.3. The Piecewise Linear Branch Predictor Using PBC Value

Further, we propose some improved *idealized piecewise linear branch predictors* (see Figures 4.7 and 4.8) that use the previous global or local branch condition (PBC) as additional prediction information. The global history length is dynamically adjusted between 18 and 48 bits and the local history length between 1 and 16 bits, as in [Jim05, Gel07a, Gel07b]. In both schemes local and global branch histories together with the PBC value are used as inputs for the selected perceptron in order to generate a prediction. The three indexes used within the weight selection mechanism are obtained through a hash function that uses three prime numbers, as follows [Jim04]:

| $index_{GH}^{i} = [(PC \cdot 511387) \oplus (PC_{i-1} \cdot 660509) \oplus (i \cdot 1289381)] \mod NW$ | (4.1) |

|--------------------------------------------------------------------------------------------------------|-------|

| $index_{LH}^{j} = [(PC \cdot 511387) \oplus (j \cdot 1289381)] \mod NW$                                | (4.2) |

| $index_{PBC}^{k} = [(PC \cdot 511387) \oplus (k \cdot 1289381)] \mod NW$                               | (4.3) |

where  $i = \overline{1, GHlength}$ ,  $j = \overline{1, LHlength}$ ,  $k = \overline{LHlength + 1, LHlength + PBClength}$  (*PBClength* is 32 in our case), and *NW* is the total number of weights (parameter varied in our simulations between 8590 and 30713). PC<sub>i-1</sub> represents the previous (i-1)<sup>th</sup> branch's PC, belonging to the path of the current branch. Consequently, a certain prediction is generated using (*GHlength* + *LHlength* + *PBClength*) number of selected weights. These weights were selected from a table containing *NW* weights. The first two relations were used according to Jimenez's simulator proposals [Jim04] while the third one was introduced by us, according to the new introduced PBC information.

#### 4.2.3.1 The Piecewise Linear Branch Predictor Using Global PBC Value

Figure 4.7 presents the scheme of the perceptron-based branch predictor that is using as additional prediction information the global previous branch condition (PBC). The lower part of the branch address (PC) selects a perceptron in the table of perceptrons and a local history register in the local branch history table.

Figure 4.7. Perceptron-based branch predictor using the global PBC value

#### 4.2.3.2 The Piecewise Linear Branch Predictor Using Local PBC Value

Figure 4.8 presents a possible scheme of the perceptron-based branch predictor that is using as prediction information local (per-address) previous branch condition (PBC). The Local Branch History Table maintains for each branch its Local History (LH) and its the Previous Branch Condition (PBC) value.

Figure 4.8. Perceptron-based branch predictor using the local PBC value

# 4.3. Experimental Results

The perceptron and our branch difference predictors were implemented by extending the *sim-bpred* simulator provided in *SimpleSim-3.0* [Sim]. We also include the implementation of the unbiased branch selection mechanism and, thus, the predictors can be evaluated on unbiased branches, too. We have evaluated our predictors on SPEC 2000 benchmarks, especially those that indicated a high percentage of unbiased branches [Gel06a, Vin06].

## 4.3.1. Evaluating State-of-the-Art Branch Predictors

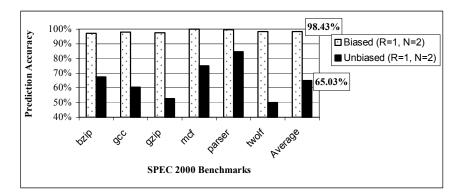

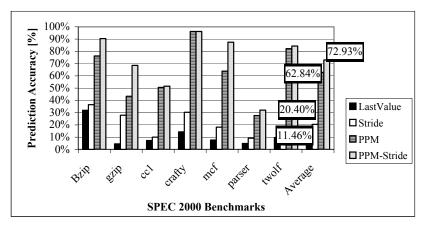

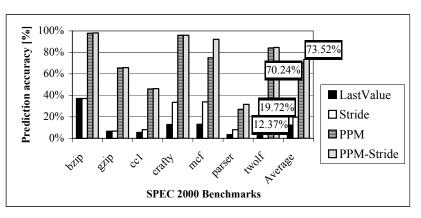

We showed that the best state of the art branch predictors [CBP04, CBP06] are obtaining very low prediction accuracies on unbiased branches, at average about 70% [Gel07b, Gel07c]. The same predictors are predicting a "normal" branch with accuracies ranging between 95% and 99%. These predictors are usually hybrid: Markovian, PPM-based, and neural. The unbiased branches cannot be accurately predicted even with the actual most powerful branch predictors. This fact is perfectly normal taking into account that the problem consists in better representing the unbiased branches in a new efficient feature space rather in finding better prediction structures.

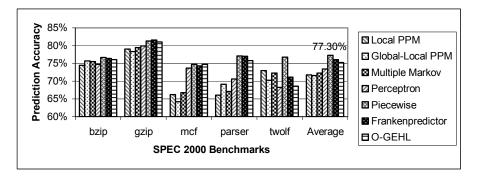

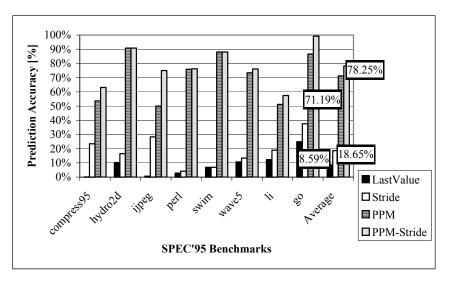

Figure 4.9. Branch prediction accuracies obtained using the perceptron-based predictors, the O-GEHL predictor and the PPM-based predictors, only on unbiased branches

As Figure 4.9 shows, the highest average prediction accuracy on the unbiased branches, of 77.30%, was provided by the idealized piecewise linear branch predictor [Jim05]. This low prediction rate is understandable taking into account that even a neural predictor cannot effectively learn unbiased branches. As a comparison, the same predictor obtained far better average prediction accuracy, of 94.92%, on all branches.

## 4.3.2. Evaluating PBC-Based Branch Predictors

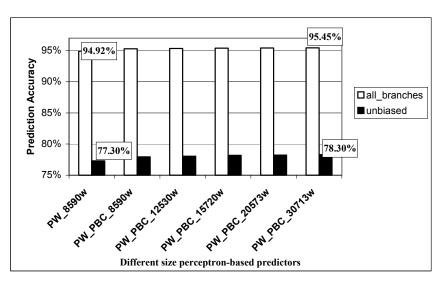

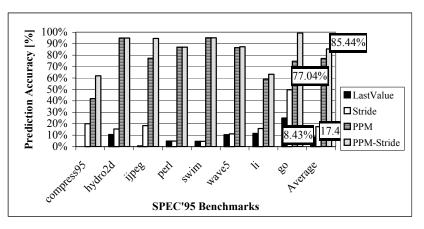

We evaluated our modified GAg, PAg and *piecewise linear branch predictor* on unbiased branches, using the global PBC value as additional prediction information. For the *piecewise linear branch predictor* we increased the number of weights from 8590 upto 30713, the higher weights number being justified by the long additional information.

With the modified *piecewise linear branch predictor* we obtained a prediction accuracy of 78.30% opposite to those obtained with the modified GAg, 69.87% and the modified PAg, 73.75%. This gain was probably obtained because both the modified GAg and PAg predictors use a hashing between PBC value and global/local branch history, while the modified *piecewise linear branch predictor* uses the branch history and PBC value without hashing (by concatenating them).

Figure 4.10 presents the prediction accuracies obtained on all branches and on the unbiased branches with our best proposed and implemented predictor: the idealized piecewise linear branch predictor using the global PBC value as additional prediction information. The first two bars represent the prediction accuracies on all branches and on unbiased branches, obtained with the idealized piecewise linear branch predictor (PW). The rest of the bars were obtained using the PBC value (32 bits) as additional prediction information, varying the number of weights (from 8590 up to 30713).

Figure 4.10. Average prediction accuracies obtained with *piecewise linear branch predictor* on unbiased branches versus all branches, using the global PBC value as additional prediction information

Analyzing comparatively the results presented in Figures 4.9 and 4.10 it can be observed how the PBC value determines the improvement of unbiased branch prediction accuracy, overcoming with at least 1% the best state of the art predictor's performance. Even if the improvement seems less significant, it is very clear how this small percentage contributes to the global prediction accuracy (value that overcomes with more than 0.53% the best state of the art predictor's performance).

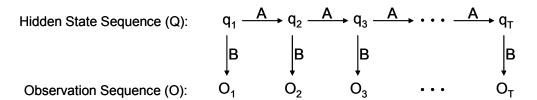

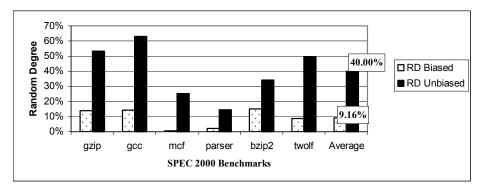

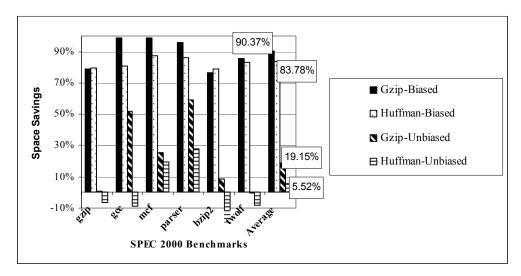

# 5. Better Understanding Unbiased Branches Using Random Degrees